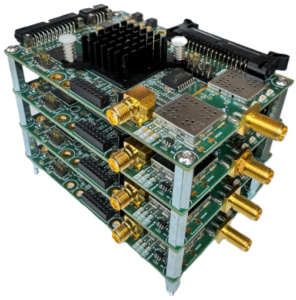

DRI-GNSS-DEV designed for testing new algorithms for GNSS receivers

It was designed for developing software-defined radio (SDR) algorithms. It enables rapid prototyping, signal discovery, and support for multiple constellations, including GPS, Galileo, GLONASS, and BeiDou.

DRI-GNNS-DEV Hardware Components:

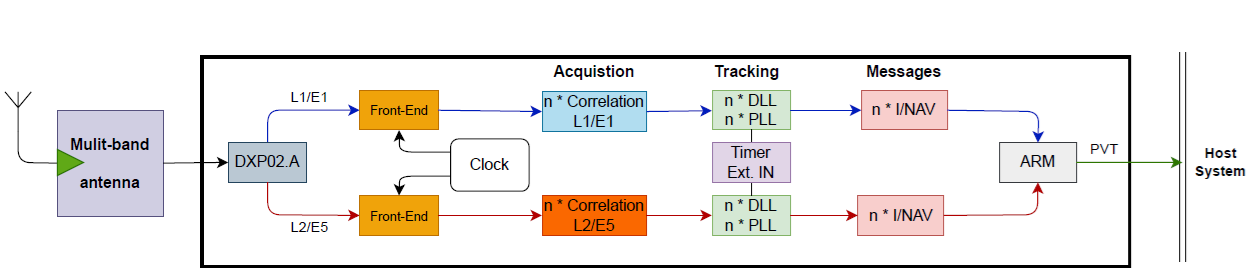

- 2 x RF Front-Ends for receiving radio waves through the antenna and converting them to digital samples (ADC),

- Intel FPGA core for fast SIS signal processing,

- 2 x ARM CORTEX M7 for calculating PVT messages (Position, Velocity, and Synchronization).

DRI-GNNS-DEV Software Components:

- Sample VHDL-based software for GALILEO signal processing including: data acquisition, satellite tracking and demodulation,

- Sample C-based software for calculating position, velocity and synchronization – PVT based on GALILEO signals.

DRI-GNSS-DEV designed to test spoofing algorithms

By combining three modules, the system can be use for testing signal interference and spoofing. It enables rapid updates and development of new PVT algorithms, jamming detection algorithms, and improved processing quality of space-based SIS signals. System is also an excellent tool for exploring the fundamentals of GNSS receiver design through practical, example-based software implementations.

Key futures:

- Testing multi-constellation Fusion algorithms,

- Analysis of SIS interferences mitigation,

- Testing of SDR algorithms,

- GNSS raw data recording,

- The ability to analyze signal jamming and spoofing.